# Применение реконфигурируемых вычислительных систем для обработки сигналов телевидения ультравысокой четкости

В.П. Дворкович, И.И. Левин, Е.А. Семерников, М.К. Чобану

Аннотация. В современных условиях, когда алгоритмы обработки и стандарты на телевидении ультравысокой четкости (ТУВЧ) находятся на стадии становления, наиболее приемлемыми для систем обработки сигнала являются реконфигурируемые вычислительные системы (РВС) на основе ПЛИС. РВС, обладая лучшими показателями эффективности, компактности и экономичности по сравнению с ЭВМ других аппаратных платформ, позволяют оптимально реализовать обработку сигнала ТУВЧ.

Ключевые слова: телевидение ультравысокой четкости, реконфигурируемая вычислительная система.

#### Введение

В первое десятилетие XXI века во всем мире активно внедряются системы цифрового телевизионного вещания и его наиболее совершенные модификации — телевидение повышенной (ТПЧ, HD) и высокой четкости (ТВЧ, HDTV). Совершенствование технологий обработки, кодирования, передачи и воспроизведения более качественной аудиовизуальной информации приводит к стандартизации еще более качественных телевизионных систем — объемного (так называемого 3D-телевидения) и телевидения ультравысокой четкости ТУВЧ (Ultra HDTV — UHDTV или Super Hi-Vision — SHV), реализующего возможности цифрового кино.

В ближайшие годы в мире ожидается пик развития ТУВЧ-индустрии. Однако активное внедрение системы ТУВЧ, в особенности стандарта 4320р с разрешением вдоль строк в 7680 пикселей и числом строк 4320, в настоящее время существенно ограничивается отсутствием высокоэффективных кодеков реального времени.

Несжатый поток информации для широко распространенного в настоящее время формата ТВЧ 1080р (в английской транскрипции HDTV) составляет до 1,9 Гбит/с, после кодирования стандартом MPEG-4/H.264 AVC [3] он сокращается до 8÷15 Мбит/с. По оценкам специалистов для формата ТУВЧ 4320р с несжатым потоком в 70 Гбит/с поток после сжатия может составить всего 24 Мбит/с, т.е. всего в среднем в два раза выше, чем для формата ТВЧ. В то же время коэффициенты сжатия для ТВЧ и для УТВЧ составляют 126÷240 раз и 2900 раз соответственно. Это обстоятельство объясняется использованием более высокой корреляции между смежными пикселями в кадре ТУВЧ и потенциальным усовершенствованием методов цифровой обработки видеоинформации и показывает, что потребная пропускная способность каналов соответствует настоящему моменту развития телекоммуникаций.

Обработка сигналов в реальном времени в современных мультимедийных системах (включая современные системы телевизионно-

го вещания, видеоконференцсвязи, системы обработки медицинских изображений и др.), в первую очередь, в системах ТУВЧ, требует высокоэффективных вычислительных платформ.

Вычислительные платформы по необходимости должны обеспечивать их адаптацию под разные алгоритмы кодеков, условия передачи, форматы, условия работы. Несмотря на значительные успехи, достигнутые в микроэлектронике, перспективные системы мультимедиа реального времени очень сложно реализовать на основе традиционных вычислительных архитектур. Для реализации системы ТУВЧ требуются специализированные архитектуры, которые должны обеспечивать не высокоскоростною обработку информации, но и быть достаточно гибкими для поддержки различных стандартов и условий работы.

В связи с этим особый интерес для построения систем обработки в реальном времени сигналов ТУВЧ представляют реконфигурируемые вычислительные системы (РВС) на основе ПЛИС, обладающие высокой реальной производительностью и свойством адаптации своей архитектуры к структуре решаемой задачи.

## Реконфигурируемые вычислительные системы

Реконфигурируемые вычислительные системы являются новым направлением в развитии суперкомпьютеров, в которых в качестве основного вычислительного элемента используются не универсальные микропроцессоры, а множество соединенных между собой ПЛИС большой интеграции, образующих единое вычислительное поле [2, 3]. В отличие от супер-ЭВМ других архитектур реконфигурируемые системы имеют возможность адаптации своей архитектуры к информационной структуре решаемой задачи или ее фрагмента, за счет чего обеспечиваются высокая реальная производительность, близкая к пиковой (не ниже 60%), и линейный рост производительности в зависимости от наращивания аппаратного ресурса. Как показали проведенные исследования [2, 3], РВС особенно эффективны при решении вычислительно трудоемких и «сильносвязанных» задач, к которым можно отнести и задачи обработки сигнала ТУВЧ. Особенно высокую эффективность РВС показывают на задачах, где требуется обработка данных нестандартных форматов, или при вычислениях с переменной разрядностью (на разных стадиях алгоритмов), что особенно актуально для цифровой обработки сигналов и, в частности, обработки сигналов ТУВЧ. В то же время РВС обеспечивают возможность обработки данных в общепринятых форматах с фиксированной запятой, а также в соответствии со стандартом IEEE-754 на операции с данными в формате с плавающей запятой одинарной и двойной точности.

РВС обладают значительно лучшими характеристиками по сравнению с многопроцессорными вычислительными системами традиционных архитектур, в частности:

- эффективность PBC (отношение «реальная производительность/пиковая производительность») выше в 4–5 раз;

- энергоэффективность PBC (отношение «реальная производительность/потребляемая мощность») выше в 2–3 раза;

- компактность PBC (отношение «реальная производительность/объем») выше в 1,5–2 раза;

- экономичность PBC (отношение «реальная производительность/стоимость») выше в 2 раза.

На задачах цифровой обработки сигналов и изображений преимущество еще выше. Этот выигрыш достигается, в том числе, за счет введения в состав ПЛИС специальных блоков, ориентированных на цифровую обработку сигналов. Так, например, одна ПЛИС XC6VSX475T семейства Virtex-6, содержащая 2016 блоков DSP48E1, работающих на частоте 400 МГц, дает производительность более 2,4\*1012 операций с фиксированной запятой в секунду (2,4 Топ/с), в то время как самые производительные DSP-процессоры фирм Analog Devices и Texas Instruments, работающие на частотах 500-1000 МГц, имеют производительность не выше  $10^{10}$  оп/с ( $10 \, \Gamma$ оп/с).

Таким образом, РВС на основе ПЛИС, обладая программируемой платформой и обеспечивая высокие показатели эффективности, компактности и экономичности, в настоящее время наиболее полно удовлетворяют требованиям, предъявляемым к вычислительным средствам обработки сигналов ТУВЧ.

## Организация вычислительного процесса в РВС

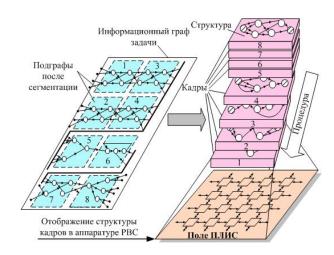

В отличие от традиционных многопроцессорных систем, у которых каждый процессор выполняет отдельную программу, вычислительный процесс в РВС заключается в аппаратной реализации в вычислительном поле ПЛИС информационного графа решаемой задачи.

Под информационным графом [4] понимается граф, вершины которого соответствуют арифметико-логическим операциям над операндами и ячейкам (каналам) памяти, в которых расположены информационные массивы. Дуги информационного графа соответствуют информационной зависимости между вершинами.

Основная идея концепции РВС заключается в аппаратной реализации всех операций, предписанных вершинам информационного графа задачи, всех каналов передачи данных между вершинами, соответствующих дугам графа, и всех информационных каналов, соответствующих входным и выходным вершинам. В этом случае задача, определенная информационным графом, будет выполнена максимально быстро, поскольку обеспечивается максимально возможное распараллеливание вычислений. Такое решение задачи принято называть *структурным* [2, 3]. При изменении задачи поле ПЛИС может быть перепрограммировано (реконфигурировано) под новую задачу.

Оптимальными при реализации РВС представляется создание большого поля ПЛИС и отображение всего информационного графа задачи на объединенный схемотехнический ресурс этого поля. Однако, как правило, это сделать невозможно практически из-за огромного количества вершин информационных графов реальных задач и из-за физических ограничений, накладываемых конструктивными и экономическими факторами на аппаратную реализацию РВС. Поэтому информационный граф задачи необходимо сегментировать на непересекающиеся подграфы определенного размера, каждый из которых может быть структурно реализован в имеющемся вычислительном поле ПЛИС.

В этом случае вычислительный процесс в РВС на основе ПЛИС организуется следующим образом. В аппаратном ресурсе РВС реализует-

Рис. 1. Процесс решения задачи в РВС

ся один из подграфов сегментированного информационного графа задачи, и на его входы из блоков памяти подаются входные данные этого фрагмента. Процесс вычисления реализуется вычислительной структурой, соответствующей данному подграфу, и на выходе формируется результат вычислений, который запоминается в соответствующих блоках памяти. Далее в аппаратном ресурсе РВС реализуется следующий подграф сегментированного информационного графа задачи, и процесс повторяется. Этот процесс показан на Рис. 1.

На рисунке номерами обозначена очередность реализации подграфов в процессе решения задачи на РВС. Очередность реализации подграфов определяется их информационной зависимостью. При этом возможны различные варианты реализации, не нарушающие информационную зависимость подграфов.

Кадр представляет собой реализованный в аппаратном ресурсе РВС подграф задачи, через который следует поток данных. Механизм последовательного обхода подграфов информационного графа задачи принято называть структурнопроцедурной организацией вычислений.

#### Аппаратная платформа РВС

Высокопроизводительные РВС строятся по модульному принципу из однотипных базовых модулей. Каждый базовый модуль содержит фрагмент вычислительного поля из ПЛИС и средства для объединения этих фрагментов в единый вычислительный ресурс [2, 3].

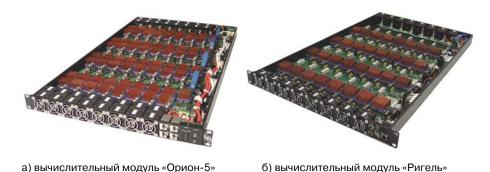

а) плата вычислительного модуля «Орион-5» на основе ПЛИС семейства Virtex 5

б) плата вычислительного модуля «Ригель» на основе ПЛИС семейства Virtex 6

Рис. 2. Платы вычислительных модулей

Рис. 3. Вычислительные модули нового поколения

В качестве примера рассмотрим аппаратную платформу высокопроизводительных РВС, созданных в НИИ МВС ЮФУ в 2010–2011 годах на основе ПЛИС семейств Virtex 5 и Virtex 6 фирмы Xilinx. С аппаратной платформой РВС более ранних модификаций можно познакомиться в [3].

Принцип открытой масштабируемой архитектуры [5], который был положен в основу разработки РВС в 2010 году, привел к появлению нового семейства вычислительных систем под названием «Орион». В рамках этих работ была создана плата модифицированного вычислительного модуля «Орион-5» с новой компоновкой и конструктивными решениями на основе ПЛИС семейства Virtex 5. В 2011 были разработаны и выпускаются платы и вычислительные модули РВС нового поколения на основе ПЛИС семейства Virtex-6. Модули выпус-

каются в двух конструктивных исполнениях — «Саиф» 6U и «Ригель» 1U, названных именами звезд из астрономического созвездия «Орион». Фотографии платы «Орион-5» на основе ПЛИС семейства Virtex 5 и платы нового поколения «Ригель» на основе Virtex-6 представлены на Рис. 2 а и Рис. 2 б.

На основе этих плат выпускаются вычислительные модули высотой 1U, на основе которых строятся PBC высокой производительности. Фотографии вычислительных модулей «Орион-5» и «Ригель» представлены на Рис. 3.

В 2011 году разработана плата вычислительного модуля ММ475, предназначенная для построения высокопроизводительных систем мониторинга телекоммуникационных сетей и обработки сигналов. Плата вычислительного модуля ММ475 обладает следующими характеристиками:

- тип ПЛИС Virtex-6 вычислительного поля XC6VSX475T-1FFG1759C;

- количество ПЛИС вычислительного поля -8;

- количество элементарных процессоров 16384;

- пиковая производительность, операций в секунду  $16.2*10^{12}$ ;

- пиковая производительность, флопс  $-1*10^{12}$ ;

- количество вх/вых LVDS (1,2 ГГц) 312;

- количество вх/вых RocketGTX (5,0 ГГц) 512;

- суммарная скорость обмена, бит в секунду  $-2.4*10^{12}$ .

Одновременно ведется проработка вариантов изделий на ПЛИС семейства Virtex-7. Ожидаемые характеристики платы вычислительного модуля ММ777 с вычислительным полем из шести ПЛИС семейства Virtex-7 XC7VX1140T-1FFG1928 и изделий на ее основе приведены в Табл. 1.

Таким образом, вычислительные модули нового поколения «Саиф» 6U, «Ригель» 1U и «Орфей» 2U на основе ПЛИС семейства Virtex-6, а также модуль ММ777 на основе ПЛИС семейства Virtex-7 открывают новые перспективы для построения вычислительных систем более высокой производительности при сохранении их стоимости.

Табл. 1. Технические характеристики изделий

### Программирование РВС

Эффективное программирование РВС является нетривиальной задачей, поскольку программировать нужно не только организацию вычислительного процесса, как это происходит в обычных многопроцессорных вычислительных системах, но и структуру РВС, адаптируя ее к структуре решаемой задачи. Традиционно считается, что программированием вычислительных структур в РВС должны заниматься схемотехники, которые с помощью САПР, предоставляемых фирмами-разработчиками (Xilinx, Altera и др.), создают аппаратные реализации алгоритмов обработки данных в схемотехническом ресурсе множества ПЛИС. Затем прикладные программисты организуют вычислительный процесс в этих вычислительных структурах. Такой способ программирования РВС по сложности разработки и эффективности получаемого технического решения сравним с разработкой специализированной вычислительной системы. Здесь достижима максимально возможная реальная производительность на уровне свыше 90-95% от пиковой производительности РВС. Но цена такой эффективности весьма высока, поскольку требуются усилия нескольких разнородных специалистов - алгоритмистов, схемотехников

| Тип платы | Число ПЛИС | Семейство ПЛИС | Интирфейс,        | Мощность, Вт | Производительность платы<br>вычислительгого модуля, Гфлопс | Производительность платы<br>вычислительгого модуля,<br>10 <sup>12</sup> операций в секунду (Ton/c) | Скорость передачи данных<br>с блоками памяти, Гбит/с | Скорость передачи данных<br>между ПЛИС, Тбит/с | Скорость передачи данных<br>между модулями, Тбит/с |

|-----------|------------|----------------|-------------------|--------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|----------------------------------------------------|

| Орион-5   | 16         | V-5            | LVDS              | 250          | 250                                                        | 5,2                                                                                                | 12,8                                                 | 1,2                                            | 1,2                                                |

| Саиф      | 8          | V-6            | GE                | 300          | 400                                                        | 8,3                                                                                                | 12,8                                                 | 1,0                                            | 0,001                                              |

| Ригель    | 8          | V-6            | GE                | 300          | 400                                                        | 8,3                                                                                                | 12,8                                                 | 1,0                                            | 0,001                                              |

| MM475     | 8          | V-6            | LVDS,<br>RocketIO | 350          | 960                                                        | 21,8                                                                                               | 12,8                                                 | 2,1                                            | 2,4                                                |

| MM777*    | 6          | V-7            | LVDS,<br>RocketIO | 350*         | 1600                                                       | 32                                                                                                 | 15,4*                                                | 2,0*                                           | 1,6*                                               |

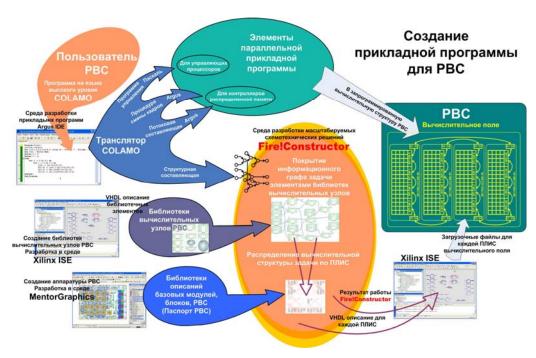

Рис. 4. Создание прикладных программ для РВС на языке COLAMO

и программистов. Однако PBC и здесь выигрывают у специализированных систем, поскольку нет затрат на создание аппаратной платформы системы — базовая аппаратная платформа PBC уже имеется. Затраты заключаются в создании в вычислительном поле PBC специализированных параллельно-конвейерных вычислительных структур, оптимально реализующих алгоритм решения задачи.

Этот метод программирования успешно применяется при создании PBC различного назначения в тех областях, где требуется получить максимальную эффективность использования аппаратных средств. В то же время в НИИ МВС ЮФУ разработан и успешно применяется новый подход к программированию PBC [3, 4].

Новый подход использует язык высокого уровня COLAMO. В этом случае вычислительная структура, создаваемая в РВС, полностью определяется программными конструкциями и структурами данных, которые использовал программист в прикладной COLAMO-программе. Масштабирование параллельных программ возможно путем изменения описания структур данных. Трансляция COLAMO-программы состоит в создании схемотехниче-

ской конфигурации вычислительной системы (структурной составляющей) и параллельной программы, управляющей потоками данных (потоковой и процедурной составляющих). Процесс создания прикладных программ для РВС и общая взаимосвязь транслятора языка СОLAMO, среды Fire! Constructor и синтезатора конфигурации ПЛИС в рамках комплекса системного программного обеспечения при создании многокристального схемотехнического решения для РВС представлены на Рис. 4.

В процессе работы транслятора формируется информационный граф прикладной задачи из текста параллельной COLAMO-программы, где операторы и функции языка по определённым правилам заменяются соответствующими блоками или группами блоков из библиотеки стандартных примитивов.

Синтезированный вычислительный граф задачи передается в среду разработки вычислительных структур Fire! Constructor для укладки на множество ПЛИС и обеспечения синхронизации между ними [7]. Одной из задач среды является сегментирование информационного графа прикладной задачи на непересекающиеся подграфы, каждый из которых будет структурно реализован в кристаллах ПЛИС выбранной РВС.

При этом вершины и дуги информационного графа заменяются примитивами ПЛИС или элементами библиотеки схемотехнических решений и интерфейсов (IP-ядер).

Применение комплекса средств разработки позволяет осуществлять трансляцию описания схемотехнической реализации информационного графа задачи на уровень логических ячеек множества ПЛИС.

Комплекс средств программирования обеспечивает производительность на уровне 60–80% от пиковой производительности системы и портирование разработанной параллельной программы на РВС других аппаратных платформ и архитектур без существенной переработки ее текста. По скорости создания прикладных программ для РВС второй подход от двух до пяти раз превосходит схемотехнический метод создания вычислительной структуры.

Следует отметить, что схемотехнический подход, как правило, применяется к программированию приложений из новых классов задач и, по мере освоения новой области, устоявшиеся схемотехнические решения переводятся в библиотеки IP-ядер и становятся доступными из языка высокого уровня СОLAMO. Таким образом, довольно быстро новые классы задач становится возможным программировать на основе второго подхода с высокой скоростью и эффективностью.

# Алгоритм кодека ТУВЧ на основе MPEG-2

Для реализации сервисов вещания телевидения ультравысокой четкости был разработан алгоритм видеокодека для эффективной передачи и записи ТУВЧ сигналов [6], который состоит из блоков преобразователя видеоформата, видеокодека и аудиокодека. Ввиду ограниченности объема статьи остановимся только на операциях преобразования видеоформата и видеокодека.

Для того чтобы закодировать ТУВЧ сигналы в формате  $Y_1Y_2CbCr$ , выполняется преобразование исходных ТУВЧ сигналов. Преобразователь видеоформата преобразует  $7680\times4320$  (G1, G2, B и R) формат в шестнадцать изображений  $1920\times1080/30$  Psf (прогрессивный сегментированный кадр), где ТУВЧ изображение делится

на пространственно-временные части. Преобразование цветового формата основано на следующем соотношении:

$$\begin{bmatrix} Y_1 \\ Y_2 \\ Cb \\ Cr \end{bmatrix} = \begin{bmatrix} 0.7152 & 0.0000 & 0.0722 & 0.2126 \\ 0.0000 & 0.7152 & 0.0722 & 0.2126 \\ -0.1927 & -0.1927 & 0.5000 & -0.1116 \\ -0.2271 & -0.2271 & -0.0458 & 0.5000 \end{bmatrix} \times \begin{bmatrix} G_1 \\ G_2 \\ R \\ B \end{bmatrix}$$

Сигнал ТУВЧ форматируется с помощью метода сдвига пикселей (pixel-offset method). Каждая компонента сигнала (G1, G2, B и R) составляет четвертую часть размера ТУВЧ и упорядочивается в соответствии со сдвигом пикселей. Так как после преобразования видеоформата получаются два сигнала яркости  $Y_1$ и У2, число значимых пикселей становится равным половине общей площади изображения ТУВЧ, равной 7680×4320. Следовательно, в случае преобразования в шестнадцать сигналов HD-SDI сигналы ТУВЧ должны быть разделены в пространственной области на восемь частей и во временной - на две части. Пространственное разделение может осуществляться в двух режимах: четыре горизонтальных части и две вертикальных части (разделение «Н»); две горизонтальных части и четыре вертикальных части (разделение «V»). Исследования показали, что более предпочтительным оказалось разделение «Н».

В качестве основной системы для первой версии кодека ТУВЧ был выбран кодек МРЕG-2 с его проверенной технологией. Видеокодек на основе стандарта МРЕG-2 состоит из четырех подкодеков для 3840×2160 изображений. Подкодек содержит четыре одноблоковых кодека ТВЧ МРЕG-2 и многоканальный синхронизатор кадров. Для сжатия больших изображений, превышающих разрешение ТВЧ с помощью видео-кодирования по стандарту МРЕG-2, необходимо разделить изображение SHV на некоторое число ТВЧ блоков.

Поскольку векторы движения в изображениях с высоким разрешением часто существенно превышают размеры векторов движения в изображениях с низким разрешением, необходима реализация в кодере оценки движения с более широким поисковым диапазоном. Поисковый диапазон векторов разрабатываемого кодера достигает ±211,5 пикселей по горизонтали

и ±113,5 пикселей по вертикали, превышая показатели существующих общераспространенных кодеров.

Оценим производительность вычислительных средств, которая необходима для выполнения сжатия сигнала ТУВЧ формата w4320p в реальном масштабе времени. За основу можно принять применяемые сейчас вычислительные мощности для кодирования ТВ сигнала высокой четкости ТВЧ формата w1080p.

Вводимые данные ТУВЧ формата w4320p примем равными 48-битам (для RGB или иной цветовой модели), по сравнению с данными ТВЧ формата w1080p, равными 24 битам, это в 2 раза больше. Разрешение ТУВЧ 8192 x 4320 в 16 раз больше разрешения для ТВЧ — 1920 x 1080. Число кадров в секунду ТУВЧ принимаем равным 100—120 кадров при тенденции перехода на 200-250 кадров, вместо 50 (100) кадров в секунду для ТВЧ — в 4 раза больше. Цветовая модель для ТУВЧ 4:4:4 вместо 4:2:0 для ТВЧ — в 2 раза больше данных.

Таким образом, суммарный поток несжатого видео ТУВЧ составляет примерно 72Гбит/с. При использовании 3D-TV поток возрастает пропорционально – в 2 раза.

Предварительная обработка может включать в себя преобразование цветовой модели и равна ~50 операций на пиксель, коррекцию геометрических и яркостных/цветовых параметров матриц (ввод осуществляется, как правило, несколькими матрицами; без устранения искажений структурой матрицы) ~ 100 оп/пиксель. Для оценки количества операций при кодировании сигнала ТУВЧ воспользуемся алгоритмами на основе MPEG-2. Используя масштабные коэффициенты, учитывающие вышеперечисленные факторы, получим, что количество операций на кадр составит примерно 18500\*10°. Формирование транспортного потока требует дополнительно 12\*10° операций.

На основании приведенных выше оценок требуемого количества вычислительных операций для обработки одного кадра телевизионного сигнала ТУВЧ можно констатировать, что для обработки сигнала в реальном времени требуются вычислительные средства с суммарной производительностью порядка  $20*10^{12}$  операций в секунду. Коммуникационные возможно-

сти системы обработки должны обеспечивать ввод потока данных со скоростью не менее 72 Гбит/с и выводить результаты обработки со скоростью 25 Гбит/с.

Осуществить подобные преобразования видеосигнала можно на ЭВМ кластерной архитектуры. Однако современный кластер такой производительности будет занимать целую стойку и иметь мощность минимум 20 кВт.

# Оценка параметров платы ММ475 для целей обработки сигналов ТУВЧ

На основании оценки производительности, пропускной способности каналов ввода/вывода и на основании данных Табл. 1 можно сделать вывод, что для создания устройств обработки сигнала ТУВЧ достаточно одной платы ММ475 на основе восьми ПЛИС семейства Virtex-6 или ММ777 на основе шести ПЛИС семейства Virtex-7.

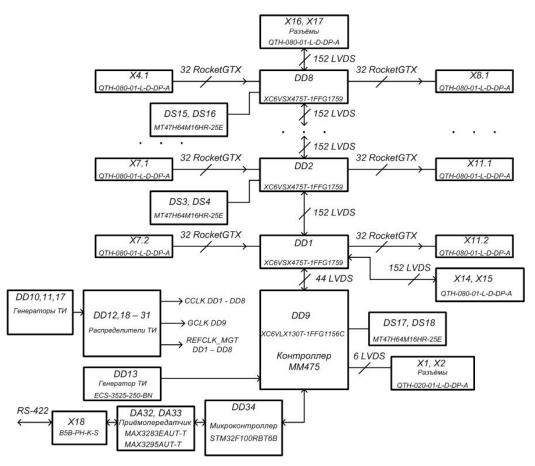

Рассмотрим структуру платы MM475, представленную на Рис. 5, с точки зрения реализации кодека ТУВЧ более подробно.

Каждая из восьми микросхем XC6VSX475Т-1FFG1759 платы ММ475 связана со смежными микросхемами сквозной магистралью из 152 LVDS-каналов, работающих на частоте до 1 ГГц. Эта магистраль используется для объединения схемотехнических ресурсов ПЛИС в единое вычислительное поле, а также для организации управления и синхронизации.

Для внешних обменов каждая ПЛИС имеет 32 входных и 32 выходных скоростных канала на основе RocketGTX, работающих на частотах до 5 ГГц. Таким образом, внешние входные данные в каждую микросхему вычислительного поля ММ475 могут приниматься со скоростью 128\*10<sup>9</sup> бит в секунду (128 Гбит/с).

Производительность ММ475, приведенная в Табл. 1, составляет 21,8 Топ/с для данных с фиксированной запятой или 960 Гфлопс для данных одинарной точности. Следует заметить, что в ПЛИС в необходимой пропорции могут сочетаться вычислительные устройства, обрабатывающие данные в различных форматах с целью обеспечения необходимой точности и динамического диапазона вычислений. Поэтому в этой же пропорции будут изменяться и приведенные выше цифры производительности.

Рис. 5. Структура платы ММ475

Входной поток сигнала ТУВЧ со скоростью 72 Гбит/с может быть разделен между восемью ПЛИС вычислительного поля на восемь потоков по 9 Гбит/с. Этого достаточно, чтобы в каждую ПЛИС в реальном масштабе времени были загружены два подкадра (из 16 подкадров) размером 1920×1080, на которые был разделен полный кадр ТУВЧ. При этом вычислительные возможности каждой ПЛИС могут обеспечить до 2,7 Топ/с или до 120 Гфлопс, что вполне достаточно для обработки данных по алгоритмам преобразования видеоформата, видеокодека в двух подкадрах.

Внутрикадровая синхронизация при объединении обработанных шестнадцати подкадров обеспечивается использованием единого системного времени.

Формирование выходного потока также не представляет трудности, поскольку каждая ПЛИС вычислительного поля ММ475 может обеспечить скорость передачи данных во внеш-

нюю аппаратуру со скоростью до 128 Гбит/с при необходимой скорости 25 Гбит/с.

Таким образом, одна плата ММ475, ориентированная на построение высокопроизводительных систем мониторинга телекоммуникационных сетей и обработки сигналов, по своим техническим параметрам вполне удовлетворяет требованиям обработки сигналов ТУВЧ в реальном масштабе времени.

#### Заключение

С точки зрения экономической целесообразности для систем обработки сигналов ТУВЧ наиболее приемлемым представляется создание специализированной микросхемы. Такое решение будет оптимальным в условиях массового выпуска бытовой и профессиональной аппаратуры обработки сигнала перспективного стандарта телевидения. Однако в современных условиях, когда алгоритмы обработки и стандарты на ТУВЧ находятся на стадии становле-

ния, наиболее приемлемыми являются программируемые вычислительные платформы, позволяющие реализовывать различные, в том числе и экспериментальные, подходы к созданию алгоритмов обработки.

Программируемые вычислительные платформы, обеспечивающие реальную производительность свыше 20 Топ/с, могут быть различными. Наиболее распространенные в настоящее время кластерные суперЭВМ, развивающие такую производительность, совсем недавно входили в список ТОР500 самых производительных суперЭВМ в мире. В 2011 году кластерная ЭВМ с такой производительностью занимает одну или две стойки, имеет потребляемую мощность порядка 20-30 кВт и стоимость 10-15 миллионов рублей. Особую проблему для кластерной ЭВМ представляет подсистема ввода данных со скоростью 72 Гбит/с одновременно во множество вычислительных узлов кластера для обеспечения параллельной обработки информации.

В свете этого плата ММ475 с производительностью 21,8 Топ/с и возможностью параллельного ввода данных с необходимой скоростью сразу во все ПЛИС вычислительного поля, имеющая мощность всего 350 Вт, выглядит наиболее привлекательной аппаратной платформой для обработки в реальном времени сигналов ТУВЧ. Программируемость аппарат-

ной платформы ММ475 позволяет реализовать практически любые стандарты обработки сигнала ТУВЧ и поставить необходимые эксперименты для отработки технических решений.

#### Литература

- ITU-T Recommendation H.264 Advanced Video Coding for Generic Audiovisual Services / ISO/IEC 14496-10

Information Technology Coding of Audio-Visual Objects Part 10: Advanced Video Coding, 2005.

- Каляев А.В., Левин И.И. Модульно-наращиваемые многопроцессорные системы со структурнопроцедурной организацией вычислений. – М.: Янус-К, 2003. – 380 с.

- 3. Каляев И.А., Левин И.И., Семерников Е.А., Шмойлов В.И. Реконфигурируемые мультиконвейерные вычислительные структуры /Изд. 2-е, перераб. и доп. / Под общ. ред. И.А. Каляева. Ростов-на-Дону: Изд-во ЮНЦ РАН, 2009. 344 с.

- Воеводин В.В., Воеводин Вл.В. Параллельные вычисления. С.-Петербург: «БХВ-Петербург», 2002. 599 с.

- Левин И.И. Реконфигурируемые вычислительные системы с открытой масштабируемой архитектурой //

Труды Пятой Международной конференции «Параллельные вычисления и задачи управления»

РАСО'2010. М.: Учреждение Российской академии наук Институт проблем управления им.

В.А. Трапезникова РАН, 2010. С.83–95.

- Дворкович В., Чобану М. Проблемы и перспективы развития систем кодирования динамических изображений // Mediavision, 2011, №№ 2–5, 7.

**Левин Илья Израилевич.** Заместитель директора по науке Научно-исследовательского института многопроцессорных вычислительных систем имени ак. А.В. Каляева. Окончил Таганрогский радиотехнический институт им. В.Д. Калмыкова в 1984 году. Доктор технических наук. Автор 230 печатных работ и 5 монографий. Область научных интересов - высокопроизводительные компьютерные системы и распределенная обработка данных. E-mail: levin@mvs.tsure.ru

Семерников Евгений Андреевич. Заведующий отделом Южного научного центра Российской академии наук. Окончил Таганрогский радиотехнический институт им. В.Д.Калмыкова в 1976 году. Кандидат технических наук. Автор 110 печатных работ и 2 монографии. Область научных интересов - высокопроизводительные компьютерные системы и распределенная обработка данных, организация параллельных вычислений, цифровая обработка сигналов. E-mail: semernikov@mvs.tsure.ru.

Дворкович Виктор Павлович. Заместитель директора Главного радиочастотного центра (ФГУП «ГРЧЦ»). Окончил Таганрогский радиотехнический институт им. В.Д. Калмыкова в 1960 году и Московский институт электронного машиностроения в 1971 году. Доктор технических наук, профессор. Автор более 200 печатных работ и 4 монографий. Область научных интересов – цифровая обработка сигналов, видеоинформационные системы. Е-mail: dvp@niircom.ru

Чобану Михаил Константинович. Заместитель начальника Управления научных исследований и разработки цифровых систем передачи информации Главного радиочастотного центра (ФГУП «ГРЧЦ»). Окончил Московский энергетический институт в 1983 году. Доктор технических наук, профессор. Автор 165 печатных работ и 2-х монографий. Область научных интересов: цифровая обработка многомерных сигналов. E-mail: tchobanou@yahoo.com